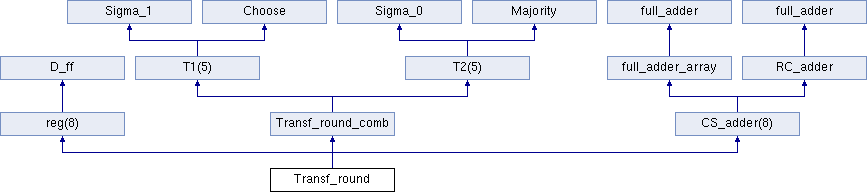

Transformation round block for the Compressor pipeline. More...

Entities | |

| Naive | architecture |

| Straightforward implementation of the transformation round. More... | |

| Precomputed_UF1 | architecture |

| Precomputed, non-unrolled architecture of the transformation round block. More... | |

| Reordered_UF1 | architecture |

| Spatially-reordered, non-unrolled architecture of the transformation round block. More... | |

| Reordered_UF2 | architecture |

| Spatially-reordered, 2-unrolled architecture of the transformation round block. More... | |

Libraries | |

| ieee | |

| Standard library. | |

Use Clauses | |

| std_logic_1164 | |

| Standard 9-values logic library. | |

Generics | |

| WORD_WIDTH | natural := 32 |

| Width of the words of the Compressor. | |

| WORDS | natural := 8 |

| Number of words required as input by the Compressor. | |

| UNROLLING_FACTOR | natural := 1 |

| Number of SHA-256 steps performed by a single round. | |

Ports | |

| clk | in std_logic |

| Clock of this component. | |

| not_rst | in std_logic |

| Active-low asynchronous reset signal. | |

| en | in std_logic |

| Enable signal. | |

| end_major_cycle | in std_logic |

| Derived pipeline clock. | |

| K | in std_logic_vector ( ( UNROLLING_FACTOR * WORD_WIDTH ) - 1 downto 0 ) |

| Constant \(K\) words. | |

| W | in std_logic_vector ( ( UNROLLING_FACTOR * WORD_WIDTH ) - 1 downto 0 ) |

| Expanded words for the current steps. | |

| input | in std_logic_vector ( WORDS * WORD_WIDTH downto 0 ) |

| Input of the compressor pipeline stage. | |

| output | out std_logic_vector ( WORDS * WORD_WIDTH downto 0 ) |

| Output of the compressor pipeline stage. | |

Detailed Description

Transformation round block for the Compressor pipeline.

This component is responsible for performing the compression function within the Compressor pipeline

Member Data Documentation

◆ clk

|

Port |

Clock of this component.

◆ en

|

Port |

Enable signal.

◆ end_major_cycle

|

Port |

Derived pipeline clock.

◆ ieee

|

Library |

Standard library.

◆ input

|

Port |

Input of the compressor pipeline stage.

◆ K

|

Port |

Constant \(K\) words.

The combinatorial block requires one constant for each step it performs within a single cycle, hence it requires a number of constants equals to the unrolling factor

◆ not_rst

|

Port |

Active-low asynchronous reset signal.

◆ output

|

Port |

Output of the compressor pipeline stage.

◆ std_logic_1164

|

Package |

Standard 9-values logic library.

◆ UNROLLING_FACTOR

|

Generic |

Number of SHA-256 steps performed by a single round.

◆ W

|

Port |

Expanded words for the current steps.

The combinatorial block requires one expanded word for each step it performs within a single cycle, hence it requires a number of expanded words equals to the unrolling factor

◆ WORD_WIDTH

|

Generic |

Width of the words of the Compressor.

◆ WORDS

|

Generic |

Number of words required as input by the Compressor.