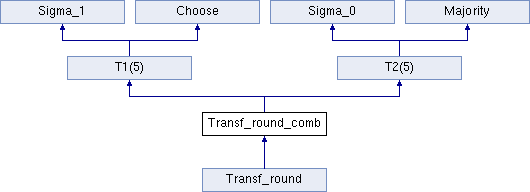

Combinatorial part of the transformation round block. More...

Entities | |

| Naive | architecture |

| Straightforward architecture of the combinatorial part of the transformation round block. More... | |

| Unrolled | architecture |

| Unrolled architecture of the combinatorial part of the transformation round More... | |

Libraries | |

| ieee | |

| Standard library. | |

Use Clauses | |

| std_logic_1164 | |

| Standard 9-values logic library. | |

| numeric_std | |

| Arithmetic library, included for the unsigned modulo addition. | |

Generics | |

| WORD_WIDTH | natural := 32 |

| Width of the words of the Compressor. | |

| UNROLLING_FACTOR | natural := 1 |

| Number of SHA-256 steps performed by a single round. | |

Ports | |

| a_in | in std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Input value of the accumulator \(A\). | |

| b_in | in std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Input value of the accumulator \(B\). | |

| c_in | in std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Input value of the accumulator \(C\). | |

| d_in | in std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Input value of the accumulator \(D\). | |

| e_in | in std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Input value of the accumulator \(E\). | |

| f_in | in std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Input value of the accumulator \(F\). | |

| g_in | in std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Input value of the accumulator \(G\). | |

| h_in | in std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Input value of the accumulator \(H\). | |

| K | in std_logic_vector ( ( UNROLLING_FACTOR * WORD_WIDTH ) - 1 downto 0 ) |

| Constant \(K\) words. | |

| W | in std_logic_vector ( ( UNROLLING_FACTOR * WORD_WIDTH ) - 1 downto 0 ) |

| Expanded message words. | |

| a_out | out std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Output value of the accumulator \(A\). | |

| b_out | out std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Output value of the accumulator \(B\). | |

| c_out | out std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Output value of the accumulator \(C\). | |

| d_out | out std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Output value of the accumulator \(D\). | |

| e_out | out std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Output value of the accumulator \(E\). | |

| f_out | out std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Output value of the accumulator \(F\). | |

| g_out | out std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Output value of the accumulator \(G\). | |

| h_out | out std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Output value of the accumulator \(H\). | |

Detailed Description

Combinatorial part of the transformation round block.

Member Data Documentation

◆ a_in

|

Port |

Input value of the accumulator \(A\).

◆ a_out

|

Port |

Output value of the accumulator \(A\).

◆ b_in

|

Port |

Input value of the accumulator \(B\).

◆ b_out

|

Port |

Output value of the accumulator \(B\).

◆ c_in

|

Port |

Input value of the accumulator \(C\).

◆ c_out

|

Port |

Output value of the accumulator \(C\).

◆ d_in

|

Port |

Input value of the accumulator \(D\).

◆ d_out

|

Port |

Output value of the accumulator \(D\).

◆ e_in

|

Port |

Input value of the accumulator \(E\).

◆ e_out

|

Port |

Output value of the accumulator \(E\).

◆ f_in

|

Port |

Input value of the accumulator \(F\).

◆ f_out

|

Port |

Output value of the accumulator \(F\).

◆ g_in

|

Port |

Input value of the accumulator \(G\).

◆ g_out

|

Port |

Output value of the accumulator \(G\).

◆ h_in

|

Port |

Input value of the accumulator \(H\).

◆ h_out

|

Port |

Output value of the accumulator \(H\).

◆ ieee

|

Library |

Standard library.

◆ K

|

Port |

Constant \(K\) words.

◆ numeric_std

|

Package |

Arithmetic library, included for the unsigned modulo addition.

◆ std_logic_1164

|

Package |

Standard 9-values logic library.

◆ UNROLLING_FACTOR

|

Generic |

Number of SHA-256 steps performed by a single round.

◆ W

|

Port |

Expanded message words.

◆ WORD_WIDTH

|

Generic |

Width of the words of the Compressor.