T2 Entity Reference

\(T_2\) step function block More...

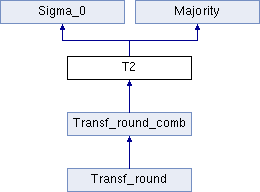

Inheritance diagram for T2:

Entities | |

| RTL | architecture |

| Architecture of the \(T_2\) step function block. More... | |

Libraries | |

| ieee | |

| Standard library. | |

Use Clauses | |

| std_logic_1164 | |

| Standard 9-values logic library. | |

| numeric_std | |

| Arithmetic library, included for the unsigned modulo addition. | |

Generics | |

| WORD_WIDTH | natural := 32 |

| Width of the words of the Compressor. | |

Ports | |

| a | in std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Input \(A\) to the step function block. | |

| b | in std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Input \(B\) to the step function block. | |

| c | in std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Input \(C\) to the step function block. | |

| o | out std_logic_vector ( WORD_WIDTH - 1 downto 0 ) |

| Output of the step function block. | |

Detailed Description

\(T_2\) step function block

This component computes the function

\[ {T_2}_t = \Sigma_0\left(A_t\right) + Maj\left(A_t,B_t,C_t\right) \quad \forall t\in\left[0,R-1\right] \]

Member Data Documentation

◆ a

|

Port |

Input \(A\) to the step function block.

◆ b

|

Port |

Input \(B\) to the step function block.

◆ c

|

Port |

Input \(C\) to the step function block.

◆ ieee

|

Library |

Standard library.

◆ numeric_std

|

Package |

Arithmetic library, included for the unsigned modulo addition.

◆ o

|

Port |

Output of the step function block.

◆ std_logic_1164

|

Package |

Standard 9-values logic library.

◆ WORD_WIDTH

|

Generic |

Width of the words of the Compressor.