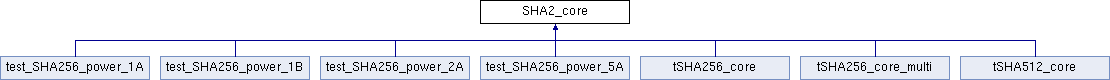

SHA-2 hash core. More...

Entities | |

| RTL | architecture |

| Architecture of the hash core. More... | |

Libraries | |

| ieee | |

| Standard library. | |

| rounds | |

| SHA-2 transformation cores library. | |

| components | |

| Basic integrated circuits components library. | |

Use Clauses | |

| std_logic_1164 | |

| Standard 9-values logic library. | |

| utils | Package <utils> |

| Package containing some generalisation functions. | |

Generics | |

| WIDTH | natural := 256 |

| Hash size. | |

| PIPELINE_STAGES | natural := 32 |

| Number of pipeline stages. | |

| UNROLLING_FACTOR | natural := 2 |

| Number of SHA-2 steps performed by a single round. | |

| PIPELINE_WORDS | natural := 14 |

| Number of words in the pipeline registers. | |

| PREFETCH_ROUNDS | natural := 4 |

| Number of round of the word prefetched from the Constants Unit and the Expander pipeline. | |

| FIX_TIME | boolean := true |

| Whether or not it is necessary to fix the timing issue. | |

| FINAL_SUM_AS_STAGE | boolean := false |

| Whether or not to perform the final sum in a separate stage. | |

Ports | |

| clk | in std_logic |

| Clock of this component. | |

| not_rst | in std_logic |

| Active-low asynchronous reset signal. | |

| en | in std_logic |

| Enable signal. | |

| start | in std_logic |

| When asserted, a new Padded Data Block to be hashed is present at input. | |

| M_blk | in std_logic_vector ( 2 * WIDTH - 1 downto 0 ) |

| Padded Data Block. | |

| iv | in std_logic_vector ( WIDTH - 1 downto 0 ) |

| Accumulators value for the provided padded data block. | |

| ready | out std_logic |

| When asserted, the circuit is able to process a new input block. | |

| completed | out std_logic |

| When asserted, the hash output is meaningful. | |

| hash | out std_logic_vector ( WIDTH - 1 downto 0 ) |

| Value of the hash of the input. | |

Detailed Description

SHA-2 hash core.

Core for applying SHA-2 on a single block message (a.k.a. Padded Data Block)

Member Data Documentation

◆ clk

|

Port |

Clock of this component.

◆ completed

|

Port |

When asserted, the hash output is meaningful.

◆ components

|

Library |

Basic integrated circuits components library.

◆ en

|

Port |

Enable signal.

◆ FINAL_SUM_AS_STAGE

|

Generic |

Whether or not to perform the final sum in a separate stage.

If the pipeline registers are placed before any adder in the transformation round, the adders of the final sum are on the critical path, hence it is beneficial to place the final sum in a separate stage. On the other hand, if the pipeline registers are placed at least after one adder, the adders of the final sum are in parallel with a portion of the transformation round, hence no longer on the critical path.

◆ FIX_TIME

|

Generic |

Whether or not it is necessary to fix the timing issue.

This flag must be set to true if the compressor stage employs the \(K\) constant(s) and the \(W\) expanded word(s) prior of the pipeline registers, since this causes a tempification issue which must be fixed; otherwise it must be set to false

◆ hash

◆ ieee

|

Library |

Standard library.

◆ iv

Accumulators value for the provided padded data block.

◆ M_blk

◆ not_rst

|

Port |

Active-low asynchronous reset signal.

◆ PIPELINE_STAGES

|

Generic |

Number of pipeline stages.

◆ PIPELINE_WORDS

|

Generic |

Number of words in the pipeline registers.

If greater than 8, an initialisation block must be defined for providing the additional initial values

◆ PREFETCH_ROUNDS

|

Generic |

Number of round of the word prefetched from the Constants Unit and the Expander pipeline.

◆ ready

|

Port |

When asserted, the circuit is able to process a new input block.

◆ rounds

|

Library |

SHA-2 transformation cores library.

◆ start

|

Port |

When asserted, a new Padded Data Block to be hashed is present at input.

◆ std_logic_1164

|

Package |

Standard 9-values logic library.

◆ UNROLLING_FACTOR

|

Generic |

Number of SHA-2 steps performed by a single round.

◆ utils

|

Package |

Package containing some generalisation functions.

◆ WIDTH

|

Generic |

Hash size.

This parameter chooses the hash function