D_ff Entity Reference

Enabled D flip-flop with asynchronous reset. More...

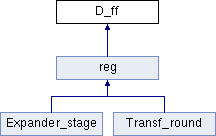

Inheritance diagram for D_ff:

Entities | |

| Behavioural | architecture |

| Architecture of the D flip-flop. More... | |

Libraries | |

| ieee | |

| Standard library. | |

Use Clauses | |

| std_logic_1164 | |

| Standard 9-values logic library. | |

Ports | |

| clk | in std_logic |

| Clock of this component. | |

| not_rst | in std_logic |

| Active-low asynchronous reset signal. | |

| en | in std_logic |

| Enable signal. | |

| d | in std_logic |

| Input signal for the flip-flop. | |

| q | out std_logic |

| Current value of the flip-flop. | |

Detailed Description

Enabled D flip-flop with asynchronous reset.

Reads its input signal and propagates it at the rising edge of the clock signal, if enables

If not enabled, retains the last sampled value

Member Data Documentation

◆ clk

|

Port |

Clock of this component.

◆ d

|

Port |

Input signal for the flip-flop.

◆ en

|

Port |

Enable signal.

◆ ieee

|

Library |

Standard library.

◆ not_rst

|

Port |

Active-low asynchronous reset signal.

◆ q

|

Port |

Current value of the flip-flop.

◆ std_logic_1164

|

Package |

Standard 9-values logic library.